納米集成電路制造工藝 CMOS邏輯電路、存儲(chǔ)器制造流程及其在計(jì)算機(jī)系統(tǒng)集成中的應(yīng)用

隨著信息技術(shù)的快速發(fā)展,納米集成電路制造工藝成為現(xiàn)代電子工業(yè)的核心。本文將從CMOS邏輯電路和存儲(chǔ)器的制造流程入手,探討其在計(jì)算機(jī)系統(tǒng)集成及綜合布線中的應(yīng)用,以幫助讀者全面理解這一先進(jìn)技術(shù)的實(shí)現(xiàn)過程與系統(tǒng)級(jí)整合。

一、納米集成電路制造工藝概述

納米集成電路制造工藝是指在納米尺度(通常指特征尺寸小于100納米)上設(shè)計(jì)和生產(chǎn)集成電路的技術(shù)。該工藝通過光刻、蝕刻、離子注入和沉積等關(guān)鍵步驟,在硅晶圓上構(gòu)建出復(fù)雜的電子元件。納米工藝的優(yōu)勢(shì)在于能夠大幅提升集成度、降低功耗并提高運(yùn)行速度,為現(xiàn)代計(jì)算設(shè)備的高性能需求提供了技術(shù)基礎(chǔ)。

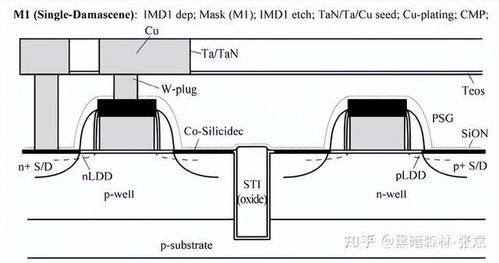

二、CMOS邏輯電路制造流程

CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)邏輯電路是現(xiàn)代集成電路的主流技術(shù),其制造流程包括以下主要步驟:

- 晶圓準(zhǔn)備:選擇高純度硅晶圓作為基底材料。

- 光刻與圖形化:使用光刻技術(shù)將電路設(shè)計(jì)圖案轉(zhuǎn)移到晶圓上,通過掩膜和光刻膠實(shí)現(xiàn)納米級(jí)精度。

- 摻雜與離子注入:通過離子注入工藝在特定區(qū)域形成N型和P型半導(dǎo)體,構(gòu)建晶體管結(jié)構(gòu)。

- 氧化與沉積:生長絕緣層(如二氧化硅)并沉積金屬層,形成柵極和互連結(jié)構(gòu)。

- 蝕刻與清洗:去除多余材料,確保電路結(jié)構(gòu)的精確性。

- 測(cè)試與封裝:對(duì)制造完成的芯片進(jìn)行功能測(cè)試,并封裝為最終產(chǎn)品。

三、存儲(chǔ)器制造流程

存儲(chǔ)器(如DRAM和NAND閃存)是計(jì)算機(jī)系統(tǒng)中的關(guān)鍵組件,其制造流程與CMOS邏輯電路類似,但具有特定優(yōu)化:

- 存儲(chǔ)單元設(shè)計(jì):針對(duì)高密度存儲(chǔ)需求,設(shè)計(jì)電容或浮柵晶體管結(jié)構(gòu)。

- 多層堆疊技術(shù):通過3D集成工藝提升存儲(chǔ)密度,例如在NAND閃存中采用多層堆疊。

- 特殊材料應(yīng)用:使用高介電常數(shù)材料提高電容性能,或采用相變材料實(shí)現(xiàn)非易失性存儲(chǔ)。

- 后端集成:將存儲(chǔ)單元與邏輯電路集成,實(shí)現(xiàn)高速數(shù)據(jù)訪問。

四、計(jì)算機(jī)系統(tǒng)集成及綜合布線

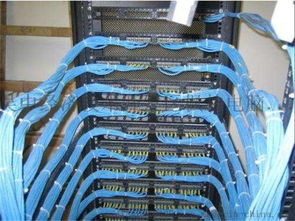

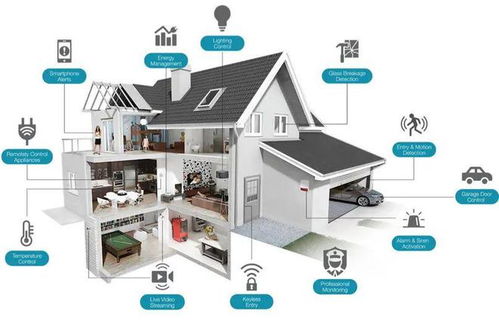

計(jì)算機(jī)系統(tǒng)集成是將處理器、存儲(chǔ)器、外圍設(shè)備等組件整合為一個(gè)完整系統(tǒng)的過程,而綜合布線則負(fù)責(zé)實(shí)現(xiàn)這些組件之間的物理連接。納米集成電路技術(shù)在此過程中發(fā)揮關(guān)鍵作用:

- 系統(tǒng)級(jí)芯片(SoC)設(shè)計(jì):通過納米工藝將CPU、GPU、存儲(chǔ)器等集成于單一芯片,減少系統(tǒng)體積和功耗。

- 高速互連技術(shù):利用納米級(jí)銅互連或硅通孔(TSV)技術(shù),實(shí)現(xiàn)芯片間的高速數(shù)據(jù)傳輸。

- 綜合布線優(yōu)化:在PCB(印刷電路板)或封裝層面,采用微細(xì)布線技術(shù),確保信號(hào)完整性和電磁兼容性。

- 熱管理與可靠性:納米集成帶來的高功率密度要求先進(jìn)的散熱方案,如微流道冷卻或熱界面材料應(yīng)用。

五、未來展望

納米集成電路制造工藝的持續(xù)進(jìn)步,如極紫外光刻(EUV)和二維材料應(yīng)用,將進(jìn)一步推動(dòng)CMOS邏輯電路和存儲(chǔ)器性能的提升。在系統(tǒng)集成方面,異構(gòu)集成和光電混合技術(shù)有望突破傳統(tǒng)布線的限制,為下一代計(jì)算系統(tǒng)提供更高效的解決方案。

納米集成電路制造工藝不僅奠定了現(xiàn)代電子設(shè)備的基礎(chǔ),還通過CMOS邏輯電路、存儲(chǔ)器制造以及系統(tǒng)集成與綜合布線的協(xié)同優(yōu)化,推動(dòng)了計(jì)算機(jī)技術(shù)的飛速發(fā)展。隨著工藝節(jié)點(diǎn)的不斷縮小和集成技術(shù)的創(chuàng)新,這一領(lǐng)域?qū)⒗^續(xù)引領(lǐng)信息產(chǎn)業(yè)的變革。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.cuncunfu.cn/product/38.html

更新時(shí)間:2026-04-18 09:49:17